I'm planning on using an SOI wafer in which I will be making 100um wide by 400um deep (till the BOx) vias, which I would then be passivating with either PECVD or Sputtered a-SiC or Oxide. It was suggested that you could help me with the supply of SOI wafers, and also with your sputter deposition services. It would be great if you could send me a quote for a box of SOI wafers with undoped Si handle and device layers, the handle being 400um thick and the device layer being as thin as you can make it. I would like the BOx to be 2-5um thick. And for the sputtering, Im looking at depositing 500A thick layer to passivate my vias. It would be nice if you could supply me information on your oxide and carbide films.

Silicon-on-Insulator (SOI) Wafers for Research & Production

What SOI Wafer Spec Do I Need?

There are many different types of silicon on insulator wafers, so how do you know which one to choose?

A scientist requested a quote for the following:

Reference RFQ#253215 for specs/pricing.

Start Researching Today! Buy Online!

It can be hard to decide which silicon on insulator soi wafer is right for your needs. Each type of bonded or simox wafer has its own advantages and disadvantages.

Our silicon on insulator wafers are the best option for most applications. We offer a variety of bonded and simox wafers, so you can find the perfect fit for your needs. Our products are backed by our commitment to quality and customer service. Buy as few as one wafer or even a diced piece!

Get your SOI Quote FAST! Or, Buy Online and Start Researching Today!

SOI Wafers to Fabricate 2D Devices

SOI wafers are composed of the wafer handles, providing mechanical strength in the manufacturing process, a device layer on/inside the device being manufactured, and a Buried Oxide layer (BOX) that separates the device layer from the handle wafers (see A). An SOI MOSFET is a metal-oxide-semiconductor field-effect transistor (MOSFET) device where the semiconductor layer, which can be either silicon or germanium, is formed over the insulator layer, which can be the buried oxide layer (BOX) formed on a semiconductor substrate.

Scientists have used the following SOI wafer for their experiments.

Item # 2551:

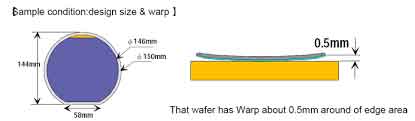

200mm SOI Type: P Dopant: B

Orientation: <100>

Resistivity: 1-20O/cm

Thickness: 725+/-25um

Device / Oxide thickness nm

70 / 2000

Buy online or send us the specs you would like us to quote.

Silicon on Insulator (SOI) Wafers

Using silicon on insulator (SOI) wafers in microprocessors is becoming more popular. These types of semiconductors are more efficient and can improve the speed and power of microprocessors. SOI wafers are relatively expensive, but they can make up for this cost in process savings. The cheapest SOI wafers are usually around 100mm in diameter, other diameters are also availalble.

We specialize in Small quantities orders!![]()

We also sell diced pieces of expensive Soitec and Simox wafers. You need to increase your semiconductor device’s performance by decreasing electrical losses. SOI wafers is the solution. SOI reduces the power required and heat that’s generated, thus increasing the device’s efficiency and speed. SOI insulation, or oxide layer, thickness depends on the application. Thermal oxide from a few nanometers thick to many microns can be used in microelectronics as it reduces short-channel effects. Silicon on insulator wafers operate at lower temperature to doping. Higher device yield can be had because of SOI’s higher density.

SOI applications include

- Silicon Photonics

- Microelectronic Devices

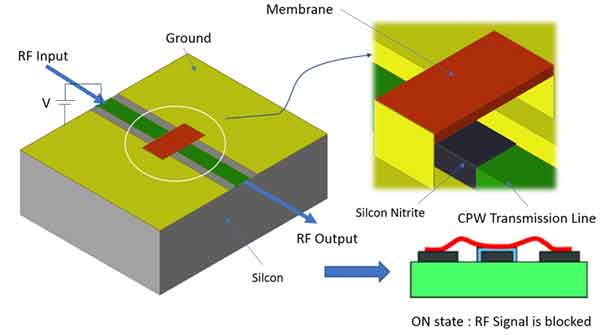

- Radio Frequency (RF) Devices

Silicon-on-Insulator for fabricating Silicon Waveguides

Researchers have been using the following specs to fabricate the following SOI wafers as there is no additional absorbtion loss due to doping in integrated photonics work.

- Silicon Waveguides

- Grating Couplers

- Integrated Photonic Components

SOI Item #3536

25mm X 25mm P/B <100> 10-20 ohm-cm 725um SSP Prime

Other wafer diameters and dimensions are also available

UniversityWafer, Inc's silicon-on-insulator (SOI) wafers , can be used the following electronics applications:

- ultra-low power signal processing

- wireless connectivity

- power, image sensors and silicon photonics applications

- radio-frequency silicon-on-insulator (RF-SOI) substrates

- ultra-low power connectivity RF

UniversityWafer, Inc. can provide researchers with a wide range of engineered substrates including fast growing segments like automotive, AI-IoT (AIoT) and 5G.

Bonded Silicon-on-Insulator for Nanomaterials Research

Researchers have used the following SOI wafer item to research nanomaterials (applied physics) for quantum/photonic computation.

Si Item #3213

150mm P/B <100> 675um SSP

Device Layer: 2um Device Res 17-23 ohm-cm

Oxide: 0.5um

Handle Layer: 675um Res 4.8-7.2 ohm-cm

SOI Wafer for Silicon Waveguides

Research clients have used our Silicon-on-Insulator wafers for their silicon waveguide research.

SOI Item #3536

25mm X 25mm P/B <100> 10-20 ohm-cm 725um SSP Prime

SOI square, Device: 220nm, BOX: 3000nm Handle thick: 725+/-15um, TTV: <1um

What Are Silicon on Insulator Applications?

Silicon on insulator (SOI) is used for many applications in electronics. These include mixed-signal applications, microprocessors, and RF waveguides. Here's a brief overview of what SOI is and how it's used. It's a promising material with many applications and is becoming more prevalent.

RF and mixed-signal applications

The global RF and mixed-signal applications of silicon on insulator market is segmented by application, region, and technology. The North American region accounts for the largest share of the industry. The growing automotive industry is a major driver. The Middle East and Africa region is expected to grow at the highest CAGR during the forecast period.

RF and mixed-signal applications of semiconductors are found in cellular technology, consumer electronics, and industrial applications. RF and mixed-signal applications require advanced manufacturing technologies to integrate passive elements with digital functionality. Embedded non-volatile memories, optical elements, and bipolar elements can be used in these mixed-signal devices.

The semiconductor on insulator technology reduces junction capacitance and power consumption, resulting in higher performance and lower power. The resulting silicon-on-insulator chips can operate up to 15 percent faster than bulk CMOS chips. The technology also increases the device's speed and power.

Silicon-on-insulator devices can be manufactured using several methods. One technique uses seed methods, which grow the topmost layer of silicon directly on the insulator. A silicon-on-insulator device is produced using a diamond-tipped tool.

The high-purity and uniformity of the semiconductor are necessary for RF devices. The thickness of the substrate is also crucial for the frequency response. Hence, the substrate and the RF components must be optimized together. However, the RF devices and the substrate specifications can vary significantly over time, so it is crucial to account for this variability when designing the device. One way to minimize the variability is to use engineered substrates.

RF waveguides

The global silicon on insulator market is segmented into three segments: technology, application, and region. In terms of region, the North American region is the largest region, accounting for approximately 80% of the total market. Europe, meanwhile, is split into three sub-regions: Italy, France, and the rest of Europe. Moreover, the Asia-Pacific region is further segmented into South Asia and Latin America. The Middle East and Africa region is likewise segmented into two segments: type and size.

The process of silicon on insulator fabrication is relatively simple and is cost-effective, requiring minimal labor and materials. It also allows for the precise control of the silicon layer thickness, which improves device performance and protection from environmental factors. These are just a few of the advantages that silicon on insulator fabrication offers.

Silicon on insulator waveguides are a promising technology for RF and optical applications. The technology has several benefits over traditional silicon waveguides, including the ability to integrate multiple functionalities on a single chip. For example, silicon waveguides can be used to build ultra-high-frequency antennas.

The silicon on insulator market is segmented by technology, application, product, and region. Automotive and consumer electronics are among the leading applications for silicon on insulators. The automotive and consumer electronics segments are experiencing rapid growth. The technology used to make silicon on insulators is very versatile and can be customized to meet specific needs of different industries.

RF amplifiers

The silicon on insulator market is segmented based on technology, region, and application. In 2018, the North American market held the largest share, followed by the European market (including the United Kingdom, France, and Italy), and the Asia-Pacific market (including Latin America and the GCC). In addition, the Middle East and Africa market is expected to witness significant growth over the next five years.

The number of transistors used in silicon on insulator (SOI) power amplifiers is limited by the breakdown voltage, which typically ranges from 80 to 300V. The breakdown voltage reduces the signal current of each transistor, which results in an improved amplifier efficiency. However, this approach is only effective when the two silicon layers have identical phase.

Another advantage of SOI technology is the ability to integrate the components within a single chip. The SOI layer eliminates the need for a metal interconnect. This helps reduce the cycle time for manufacturing products. SOI technology is also capable of reducing RF losses significantly.

Another benefit of SOI technology is the ability to make high-frequency devices. RF amplifiers using SOI devices need wideband power, and SOI technology is ideally suited for this purpose. In order to achieve this, dynamically-biased silicon transistors are used in stacks with different topologies. This reduces gate oxide breakdown and improves output power. Moreover, the power performance of SOI devices is enhanced by the incorporation of series-connected transformers.

RF transceivers

SOI is an excellent choice for RF transceivers due to its superior performance characteristics. It offers superior insertion loss and linearity while providing CMOS efficiency and a low power envelope. In addition, it enables faster data transmission for applications such as vehicle-to-vehicle communications and virtual reality. Furthermore, it is cost-effective and allows for the stacking of multiple power amplifiers in a single chip.

The process for silicon on insulator devices is based on a two-layer process. The first layer is oxidized, while the second layer is deposited on top. This step-by-step process is referred to as Smart Cut, and involves controlled exfoliation and ion implantation.

The second layer consists of a transistor and a capacitor. These are connected serially. This enables the device to have an integrated transmitter and receiver. Additionally, it has body-bias capability, which allows it to provide superior performance and energy efficiency. It also offers superior reliability in automotive applications.

SOI provides high resistivity properties, which helps reduce substrate losses. It can reach values as high as 1 kO*cm. This makes SOI a promising substrate for RF integrated circuits and mixed-signal applications. In addition, its low-power consumption and wide-band capability make it a valuable choice for mobile electronics and other RF transceivers.

CMOS technology is another option for RF transceivers. It allows for multiple active devices and has a high-Q factor. In addition, the process also enables high-value poly resistors, high-current inductors, and MOM capacitors.

Radio Frequency (RF) Filters

RF filters using silicon on insulator (SOI) technologies have several advantages over conventional RF filters. This technology allows for small footprints, high power handling, and an extensive tuning range. It also has the advantage of avoiding the nonlinearities of varactor filters and the size limitations of switched filter banks. This type of RF filter can also be programmed via a three-wire serial control interface. Its features include a five-bit tuning resolution, center frequency and bandwidth tuning, and reflection coefficient tuning. In addition to these advantages, the power consumption of this type of RF filter is less than 50 mW.

RF filters using SOI substrates can also be mounted as flip-chip components. The flip-chip mounting method helps minimize signal loss that occurs between the SOI substrate and the filter. This type of mounting also allows for higher performance and reduced parasitics. In addition, SOI substrates are inexpensive and are suitable for use in devices with high sensitivity.

A thin layer of silicon is used as the core of the filter. The SOI layer has a high refractive index and a small footprint. It is also capable of multifunctionality on a single chip. However, silicon waveguides are sensitive to fabrication defects and sidewall roughness, which can increase the loss and induce phase error.

Video: Silicon on Insulator Tech

Silicon-on-Insulator Applications

SOI applications include:

- RF Filters

- Optoelectronics

- Image Sensing

- Wireless Connectivity

- Flexible-Hybrid Electronics

- RF MEMS

End Markets Include:

- Telecommunications

- Consumer

- Power

- Medical

- Microfluidic Devices

What are Common SOI Wafer Specs Used to Fabricate Microfluidic Devices

A process integration engineer need to find the right soi wafer specs for microfludic device fabrication. He requested we quote the following:

- check autofluorescence of the material in an inverted microscope so small pieces or 2" wafers, relatively thin box, ok

- whole wafers for processing with thick box so we can remove all the Si substrate (backgrind??) and end up with ~100um thickness chips with device layer (~500 nm Si) on oxide (the box of the SOI wafer).

Reference #251891 for specs and pricing.

Why Use SOI Wafers to Fabricate Microfluidic Devices?

Silicon on insulator (SOI) wafers have become the most commonly used substrate for microfluidic dev. This is because they provide a number of advantages for the fabrication of these chips. The main advantage is that they improve the speed and efficiency of the chip. The other advantage is that they have a high device yield.

The SOI insulating oxide is then bonded to the upper silicon layer via bonding technology. This process typically uses ion implantation to create the insulating oxide layer directly under the silicon surface and exfoliation to control the thickness of the silicon layer.

These processes allow the silicon layer to be precisely etched, which ensures that it is uniformly etched. The etching rate varies from 0.8 mm/min to 1.25 mm/min depending on the width and aspect ratio of the cavities.

For microfluidic dev, this type of SOI insulating oxide is often used in conjunction with Dry Reflow Etching (DRIE). DRIE etching removes very precise amounts of silicon to create the desired cavities defined by a photomask.

This method is very easy and allows for the precise control of the silicon layer thickness, which improves device performance and reduces environmental exposure. The resulting device is also less power-hungry than similar devices fabricated on traditional silicon substrates. This is especially important for low-power applications. SOI insulators are also known for their ability to form a low-loss waveguide in RF and optical applications.

SOI Rib Waveguide

A masters student requested the follwoing quote:

I have checked them, and I think that SOI with ID 1811 is suitable for us, but the SOI thickness is only 220 nm. We just wondering that too thin for our research, because we will use SOI rib waveguide with the total thickness is around 400 nm or 500 nm (the detail design as attached file).

For the future project, we also want to add the grating (pitch grating around 254 nm) in the SOI rib waveguide.

So, is it possible if we will order with the grating layer in the SOI waveguide?

The second question is could the university wafer also build the SOI active layer? or is it special only for SOI passive layer?

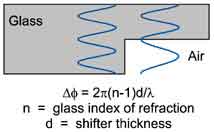

A Silicon-on-Insulator (SOI) rib waveguide is a type of optical waveguide that is widely used in silicon photonics due to its ability to tightly confine light. It's based on the SOI technology, a type of fabrication method used in semiconductor industry where a thin layer of silicon (the top layer) is placed on an insulator, typically Silicon Dioxide (SiO2).

The term "rib" refers to the specific structure of the waveguide. The rib waveguide is a ridge or a "rib" of silicon that sits on top of the silicon layer, surrounded by the insulator, creating a three-layer structure: silicon (rib) - silicon - insulator.

The light is guided down the silicon rib, and because of the refractive index difference between the silicon and the insulator, the light is effectively confined within the silicon rib. This allows for efficient transmission of the light with low losses.

SOI rib waveguides are often used in various integrated optical circuits, including modulators, detectors, multiplexers, etc. due to their high performance and compatibility with existing silicon-based manufacturing techniques.

Reference #237913 for specs and pricing.

What is SOI Passive Layer?

in a Silicon-on-Insulator (SOI) technology, the "passive" layer typically refers to the insulator layer, which is often composed of silicon dioxide (SiO2) or some other material with a low refractive index. This layer is called "passive" because it does not actively participate in guiding the light (as the silicon "rib" does in a waveguide) or in electronic conduction, but it plays a critical role in the overall device structure and performance.

The SOI structure is usually a three-layered stack: a thin silicon layer (the device layer where the active devices like transistors or waveguides are built), the insulating layer (also known as the buried oxide or BOX layer), and a thicker silicon layer (the substrate or handle layer).

The role of the passive (insulating) layer in the SOI technology is to electrically isolate the top thin silicon layer (where the active devices are located) from the bottom silicon substrate. This isolation can improve the performance of the active devices, reduce power consumption, and mitigate various parasitic effects often encountered in traditional silicon technologies. In terms of optical waveguides, the insulator layer also helps confining the light within the guiding layer (top silicon layer), providing efficient light transmission.

SAVE on Expensive Soitec SOI SOITEC SOI Wafers and Simox SOI wafers DICED into small and affordable pieces!

Bonded SOI Wafers made to order in small quantiles and short lead times.

We work with several SOI manufacturers to provide small quantities of SOI to you. Whole wafers and diced pieces available at a deep discount

For example we have a potential order for 50 of the following:

100mm P/B (100) 500um 10-20 ohm-cm Prime Grade

Device 340nm

Oxide 1,000nm

The manufacturer's minimum quantity is 50 wafers. But you only need say 1-3 wafers. We could potential buy 50 and sell you just a few at a very reasonable cost.

Other diameters such as 150mm is also possible. If this interests you, please let us know. Or fill out the form below and let us know which specs you need!

Below are just some of our Thin Device Layer SOI Inventory

| ID | Diam | Type | Dopant | Orien | Res (Ohm-cm) | Thick (um) | Polish | Grade |

Device: 220 nanometers, BOX: 3000nm Handle thick: 725+/-15um, TTV: <1um |

||||||||

| 3536 | 25mm X 25mm | P | B | <100> | 10--20 | 725um | SSP | Prime |

Device 2.2um BOX, 27.5 micron Device. Handle Res: 1000-2000 ohm-cm, Device Res: 0.004-0.006 ohm-cm |

||||||||

| 3308 | 100mm | P | B | <100> | 1000-2000 | 483um | SSP | Prime |

Device Layer: 2um, Oxide: 0.5um, Handle Layer: 675um. Device Res 17-23 ohm-cm, Handle Res 4.8-7.2 ohm-cm |

||||||||

| 3213 | 150mm | P | B | <100> | 10--20 | 675um | SSP | Test |

Device Layer: 220nm, Oxide: 2um, MFR PN: SMB-6P675-2-0.22 |

||||||||

| 3381 | 150mm | P | B | <100> | 10--20 | 675um | SSP | Prime |

Device thickness: 70nm, Oxide thick: 2000nm |

||||||||

| 2551 | 200mm | P | B | <100> | ~1-20 | 725um | SSP | Prime |

Device: 220nm, BOX: 3,000nm |

||||||||

| 3523 | 200mm | P | B | <100> | 10--20 | 725um | SSP | Prime |

SIMOX Silicon-on-Insulator SOI

We have the following thin device layer SOI available in small and large quantities. Please fill out the form for an immediate quote.

100mm SOI WAFERS

SOI DEVICE TOP LAYER:

Diameter: 100±0.2mm

Type/Dopant: P/B

Orientation: (1-0-0)±0.5°

Thickness: 220±10nm

Resistivity: 8.5-11.5 ohm-cm

Finish: Frontside Polished

SOI BURIED THERMAL OXIDE:

Thickness: 3μm±5%

SOI HANDLE LAYER:

Diameter: 100±0.2mm

Type/Dopant: P/B

Orientation: (1-0-0)±0.5°

Thickness: 725±15um

Resistivity: ≥750 ohm-cm

Notch: Semi Standard

Back Finish: Etched + Oxide

Overall Wafer:

Edge exclusion: ≤5mm

TTV: ≤5μm, Warp: ≤50μm, Bow: ≤50μm

150mm SOI WAFERS

SOI DEVICE TOP LAYER:

Diameter: 150±0.5mm

Type/Dopant: P/B

Orientation: (1-0-0)±0.5°

Thickness: 220±10nm

Resistivity: 8.5-11.5 ohm-cm

Finish: Frontside Polished

SOI BURIED THERMAL OXIDE:

Thickness: 3μm±5%

SOI HANDLE LAYER:

Diameter: 150±0.5mm

Type/Dopant: P/B

Orientation: (1-0-0)±0.5°

Thickness: 725±15um

Resistivity: ≥750 ohm-cm

Notch: Semi Standard

Back Finish: Etched + Oxide

Overall Wafer:

Edge exclusion: ≤5mm

TTV: ≤5μm, Warp: ≤50μm, Bow: ≤50μm

What SOI Wafers Are Used in Lab Research to Fabricate Silicon Nano Membrane Photodiode?

The process for forming and transporting a partially- or fully-formed photodiode multilayer structure on a flexible array substrate may be performed starting from a semiconductor-on-insulator substrate (SOT) comprising an attached wafer, a buried oxide (BOX) layer, and a thin layer of monocrystalline semiconductor (a device layer). Removing the handle wafer releases the photodiode multilayer structures along with the device layer and buried oxide layer upon which they are formed, and allows the released structures to be transferred to and attached to a flexible array substrate, for example, a polymeric film.

Researchers have used the following SOI wafers for their photodiode research:

200mm SOI

Device Layer: 55nm

Oxide: 145nm

1-10 ohm-cm 500um DSP

Silicon on Insulator Informational Video

Watch https://www.youtube.com/embed/0hkm3iw7MkI

devices. They are crucial in the production of smart power devices, microprocessors, and optoelectronic circuits. The technology is also used for miniature LCDs and high resolution displays. Here are some of the benefits of SOI. Aside from its low-cost, high-quality and flexible design, SOI wafers are extremely easy to manufacture.

devices. They are crucial in the production of smart power devices, microprocessors, and optoelectronic circuits. The technology is also used for miniature LCDs and high resolution displays. Here are some of the benefits of SOI. Aside from its low-cost, high-quality and flexible design, SOI wafers are extremely easy to manufacture. lithography is illustrated in FIG. 25, which is a plan view of a generic phase shift mask blank. The exposure pattern shown in FIGS. 28 and 29 is at right angles to each other and is a double exposure pattern. As an alternative to a single exposure pattern, the method may include a chromeless phase-shift reticle. The features 36 on the photoresist are printed to match the phase-shifting patterns.

lithography is illustrated in FIG. 25, which is a plan view of a generic phase shift mask blank. The exposure pattern shown in FIGS. 28 and 29 is at right angles to each other and is a double exposure pattern. As an alternative to a single exposure pattern, the method may include a chromeless phase-shift reticle. The features 36 on the photoresist are printed to match the phase-shifting patterns. contact with layers of photoresist. The binder is produced by casting prepolymers on a poly(dimethylsiloxane) matrix and then curing the material. The presence of a refractory phase allows the Binary Elastomeric Mask to exploit proximity and near field optical effects.

contact with layers of photoresist. The binder is produced by casting prepolymers on a poly(dimethylsiloxane) matrix and then curing the material. The presence of a refractory phase allows the Binary Elastomeric Mask to exploit proximity and near field optical effects. RF filters are passive coaxial components. They have three basic varieties: linear, nonlinear, and time-invariant. These components allow some frequencies to pass and reject others. Several common frequency bands are covered by different types of RF filters. Among them are WiFi, Bluetooth, GPS L1, and ISM. Several other types are available for specific applications, such as EMI/RFI filters, as well as a range of other less common frequencies.

RF filters are passive coaxial components. They have three basic varieties: linear, nonlinear, and time-invariant. These components allow some frequencies to pass and reject others. Several common frequency bands are covered by different types of RF filters. Among them are WiFi, Bluetooth, GPS L1, and ISM. Several other types are available for specific applications, such as EMI/RFI filters, as well as a range of other less common frequencies.

devices, from traffic lights and LEDs to information displays, optical fiber, and more. The most common devices involving light and electricity are LEDs, photo diodes, and solar cells. The science behind these devices is a vastly fascinating area of study. To learn more about optoelectronics, read on.

devices, from traffic lights and LEDs to information displays, optical fiber, and more. The most common devices involving light and electricity are LEDs, photo diodes, and solar cells. The science behind these devices is a vastly fascinating area of study. To learn more about optoelectronics, read on.