Silicon Wafer Bonding Service for Research & Production

Silicon Wafer Bonding Services

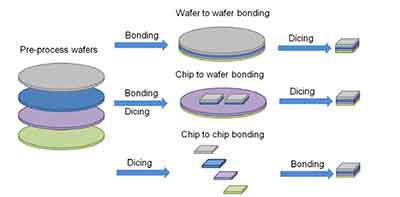

Wafer bonding is a process used to attach one wafer to another. The two wafers need to be placed in a horizontal position and the topography of the two wafers might differ dramatically. Therefore, the package assembly process needs to take these variations into account. However, there are several ways to accomplish this. Here are the most common methods.

UniversityWafer, Inc. can help you with all your bonding needs. Get Your Quote FAST!

What are Wafer Bonding Techniques

There are several wafer bonding methods that we have available for clients. Please provide your specs and quantity for an immediate quote.

Direct Wafer Bonding

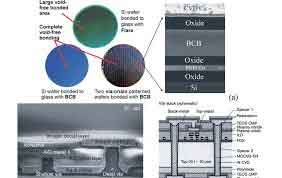

Direct silicon bonding, also called silicon fusion bonding, uses mechanical force and high temperatures of greather than 700 degree celsius to bond two silicon wafers together. Other substrates can also use the direct bonding technique including glass.

Anodic Wafer Bonding

Anondic bonding uses an electrical field that is between 200-1000 Volts to bond silicon to glass wafers lik Borofloat 33 at temperatures ranging from 180 to 500 degree celsius. Does not work with an oxide layer.

Adhesive Wafer Bonding

A low temperature bonding often used for surface planariztion and particle toleration.

Sapphire Wafer Bonding for Dry Etching Researcher requested the following quote:

"The application is as a carrier wafer in dry etching – however the 1300 micron thickness might cause issue with our clamping system.

Though it might be too much for a carrier wafer!

Can you offer a wafer closer to the 675 micron standard Sil wafer thickness? If not, what is the pricing for a 6 inch, 600 micron SOI?

We are also interested in the thinned silicon wafers but have concerns about its mechanical strength & handling in clamps. Both might be addressed if there is a process for bonding & debonding to a carrier wafer 525 microns thick – so it would have the standard 675 micron overall thickness."

For Dry Etching UniversityWafer, Inc. Quoted:

Pls see below for the offer on each type of wafer,the thinner for your dry etching purpose

- 150mm SiC wafers 4H N-type 350+/-25um double sides polished

- 150mm sapphire wafers C-Plane,500+/-25um,Both sides polished

- 200mm sapphire wafers C-Plane,725+/-25um,Both sides polished

- 150mm Thin silicon wafers 150 microns thick,double sides polished

- HOPG substrate,size: 10x10x1mm substrate , misorientation >1.5deg,Purity >4N

For Bonding:

2-1. 150mm sapphire wafers C-Plane,1300+/-25um,Single side polished,Qty. 1

Reference #267923 for pricing

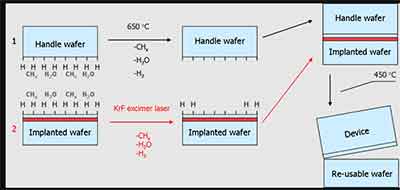

Direct & Temporal Silicon Wafer Bonding

Direct bonding mainly used to fabricate high-performance silicon wafers, including semiconductors, PVs, and solar cells. The temporal silicon wafer bonding is specifically designed for semiconductor production. It is compatible with high-temperature, high-vacuum processes, typical process chemicals, and low-k dielectric materials. Temporal bonding technology limits the number of crystal defects introduced to a silicon wafer in a process, since virtually no mechanical forces are required to initiate a wafer bonding effect.

- bonding wafers

- wafer bonding

- wafer surfaces

- wafer molecules

- silicon wafers

- dielectric materials

- binding silicon

- bonded silicon

- temperature wafer

- wafer pair

- complete wafers

- porous silicon

- clean wafers

- wafer stack

- oxidized silicon

Bonding Fused Silica Wafers

Scientist was asking for the following quote:

"We would like to purchase 25 qty 6" fused silica wafers (double side polished). Would like to know the melting point and RI @ 630nm with the quote.

We are looking for a special wafer- single crystalline silicon on top of fused silica or quartz or a glass wafer (with high melting point. A thin single crystal silicon layer bonded to a fused silica wafer will work also. Do you have such wafers or can you customize/produce such wafers for customers?"

UniversityWafer Quoted:

150mm 500um JGS1 <1nm Ra 40/20 Scratch/Dig RI@630nm is 1.457 and the transmission from 500 to 680n is more than 95%

Reference #256899 pricing pricing

What Is Wafer To Wafer Bonding?

What is wafer to wafer bonding? This is a process used to attach a wafer to another. The wafers need to be placed in a horizontal position. In addition, the topography of the two wafers might differ dramatically. Therefore, the package assembly process needs to take these variations into account. However, there are several ways to accomplish this. Here are the most common methods.

Wafer to wafer bonding is a packaging technology that ensures hermetically sealed encapsulation. Its  diameters range from 100 mm to 200 mm, or about four to eight inches. In the early days of the microelectronics industry, wafers were smaller, about one inch in diameter. The bonding technology used must match the substrate and gaseous atmosphere.

diameters range from 100 mm to 200 mm, or about four to eight inches. In the early days of the microelectronics industry, wafers were smaller, about one inch in diameter. The bonding technology used must match the substrate and gaseous atmosphere.

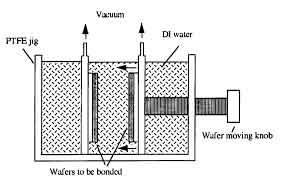

If the wafers are not identical, they are bonded by either dipping in buffered HF or cleaving with a diamond scribe. A wafer pair that is not bonded will have voids and is unable to function properly. The other way to test a bond is to use a razor edge inserted into the space between the two. A dicing saw will then be used to cut the pair apart.

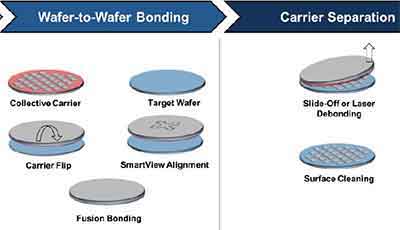

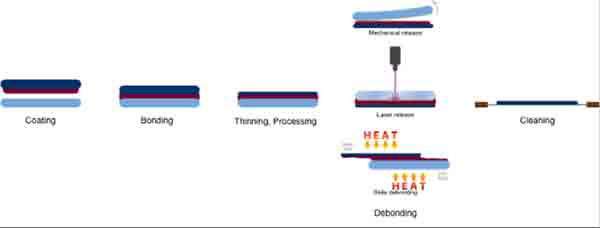

The different types of bonding are based on the materials being used. In some cases, the wafers are bonded to temporary carrier substrates, but this process is usually done after they have been debonded from them. While this method is more commonly used in semiconductor applications, it is also preferred in some manufacturing processes. It offers higher throughput, as well as a simpler way to align the different layers of the semiconductor.

When a wafer is bonded to a temporary carrier substrate, it must be debonded and then bonded again. In some cases, the process is front-attached, which allows for frontside processing. In other cases, the carrier is back-attached, which allows for backside processing to be performed. In other cases, the carrier is attached to a permanent carrier and is separated afterwards.

Before the bonding process, the wafers must be properly prepared. This is the only way to achieve the best results. This process is often used for high-tech devices, but it is important to note that the process sequence is different for different types of semiconductor wafers. It is important to make sure the substrate is suitable for the processing method you are using. It is also important to consider the type of carrier you are using. If you're using front-attached carriers, you can process the backside while the carrier is attached to the backside.

The process itself depends on the type of wafers. If you're using temporary carriers, you can attach the wafers to the carriers using a glue or another material. You can then separate the wafers once you have bonded them. Once you've bonded the two pieces of the stack, the process can begin. In some cases, it's necessary to process both sides of the stack.

Wafer to wafer bonding is done by ensuring that the two layers of the semiconductor are properly aligned. This is necessary for the process to be successful, otherwise, the components will slide off. The process is also critical for the quality of the final product. If the two layers don't align correctly, you won't be able to get the desired results. But it does require precision and high-quality products.

When using the eutectic state, the metals that are bonded are in liquid phase, resulting in a planarized surface. The liquid state of the interface provides good tolerance for particle size and topography. The materials are permanently connected. The process is a crucial step in semiconductor manufacturing. The process can be costly and may result in errors. By choosing the right material and the right adhesives, you can create a high-quality product.

This process requires two wafers to be bonded together. It has many benefits, including high flexibility. It also allows for high-bandwidth memory. Unlike the previous method, the eutectic method is low-temperature. And it can be used to make a semiconductor product, which has a high-performance price. It's a great way to reduce costs in manufacturing and improves manufacturing.

and silicon are placed above one another. In order to create an anode, an electrode is used. This can be a needle, a full-area cathode electrode, or a chuck. During the process, the glass acts as the anode while the chuck is the cathode.

and silicon are placed above one another. In order to create an anode, an electrode is used. This can be a needle, a full-area cathode electrode, or a chuck. During the process, the glass acts as the anode while the chuck is the cathode. process, chemical bonds are formed between molecules of a substrate. The adhesion strength of direct wafer bonding is typically low at room temperature. The maximum strength of the bonds is achieved by thermal annealing at a high temperature. In order to get the maximum bond strength, the surface needs to be highly pristine.

process, chemical bonds are formed between molecules of a substrate. The adhesion strength of direct wafer bonding is typically low at room temperature. The maximum strength of the bonds is achieved by thermal annealing at a high temperature. In order to get the maximum bond strength, the surface needs to be highly pristine. temperature. A plasma pretreatment removes organic contamination from the wafer surface. Another method is hydrophilic bonding, which uses a thin layer of water on a glass carrier. This method is effective because it is low-temperature and can be done without high-temperature equipment.

temperature. A plasma pretreatment removes organic contamination from the wafer surface. Another method is hydrophilic bonding, which uses a thin layer of water on a glass carrier. This method is effective because it is low-temperature and can be done without high-temperature equipment.